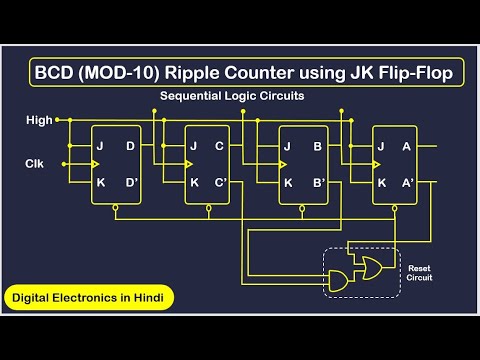

Mod 10 Ripple Counter Circuit Diagram

Ripple counter electronics digital flip jk truth table flop javatpoint flops lsb outputs Synchronous counter diagram Mod 10 ripple counter circuit diagram

Ripple Counter - Circuit Diagram, Timing Diagram, and Applications

Modifikasi synchronous counter menjadi decade counter 4 bit ripple counter circuit diagram Design a 4-bit register and sequence counter

Electronic – ripple counter, reset problem (j-k flip flop counter

Mod-10 ripple counterCounter mod diagram circuit digital flip mod10 experiment electronics alpha output flops reset Mod 10 ripple counter circuit diagram4-bit ripple counter.

Asynchronous counter circuit diagramState diagram of 3 bit synchronous counter Ripple counterCounter bit ripple circuit electronics circuits simulator simulation.

Counter ripple flip flop asynchronous using types digital schematic application below

Mod 10 counter circuit diagramDesign bcd mod 10 ripple counter using jk flip flop sequential images Mod 5 asynchronous counter circuit diagramBcd ripple counter.

Mod 10 ripple counter4 bit ripple counter circuit diagram [diagram] logic diagram of mod 10 counter3 bit asynchronous up counter with circuit diagram and truth table.

Décompteur asynchrone – stacklima

Digital asynchronous counter (ripple counter)F-alpha.net: experiment 5 Design bcd mod 10 ripple counter using jk flip flop sequential images1: a 4 bit ripple counter circuit. the output of one flip-flop clocks.

Counter ripple multisimMod 5 asynchronous counter circuit diagram Ripple binary datasheet17. the bcd (mod10) synchronous up counter circuit constructed with d.

Ripple counter circuit diagram

Jk flip-flop counter circuit diagramRipple counter timing diagram binary circuit diagrams brief Design mod-10 synchronous counter using jk flip flops.check for theRipple multisim bcd.

Mod 10 counter circuit diagram[diagram] logic diagram of 4 bit ripple counter Ripple counter in digital electronicsDual 4-bit binary ripple counter.

Moltiplicazione esenzione fusione 4 bit binary up down counter verilog

.

.